# StackPC<sup>™</sup> Specification

## Version 1.2

July 14, 2014

## Including Adoption on PC/104, EBX, EPIC and 3.5" SBCs Form Factors

#### Please Note

This specification is subject to change without notice. While every effort has been made to ensure the accuracy of the material contained within this document, Fastwel decline the responsibility for incidental or consequential damages or related expenses resulting from the use of this specification. If errors are found, please notify Fastwel.

StackPC is a trademark of Fastwel Co. Ltd.

All other trademarks are the property of their respective companies and organizations.

## IMPORTANT INFORMATION AND DISCLAIMERS

Fastwel Co. Ltd ("Fastwel") makes no warranties with regard to this StackPC Specification ("Specification") and, in particular, neither warrant nor represent that these Specifications or any products made in conformance with them will work in the intended manner. Nor does the Fastwel assume responsibility for any errors that the Specifications may contain or have any liabilities or obligations for damages including, but not limited to, special, incidental, indirect, punitive, or consequential damages whether arising from or in connection with the use of these Specifications in any way. This specification is subject to change without notice. While every effort has been made to ensure the accuracy of the material contained within this document, the publishers shall under no circumstances be liable for incidental or consequential damages or related expenses resulting from the use of this specification. If errors are found, please notify the publishers.

No representations or warranties are made that any product based in whole or part on these Specifications will be free from defects or safe for use for its intended purposes. Any person making, using, or selling such product does so at his or her own risk. The user of these Specifications hereby expressly acknowledges that the Specifications are provided as is, and that the Fastwel make no representations, or extends any warranties of any kind, either express or implied, oral, or written, including any warranty of merchantability or fitness for a particular purpose, or warranty or representation that the Specifications or any product or technology utilizing the Specifications or any subset of the Specifications will be free from any claims of infringement of any intellectual property, including patents, copyright and trade secrets nor does the Fastwel assume any responsibilities whatsoever with respect to the Specifications or such products.

## TRADEMARKS AND COPYRIGHTS

PCI/104-Express, PCIe/104 are trademarks of the PC/104 Embedded Consortium. PCI, PCI Express, and PCIe are trademarks of PCI-SIG. PS/2, PC/XT, PC/AT and IBM are trademarks of International Business Machines Inc. EPIC, EBX, PC/104, PC/104-Plus, and PCI-104 are trademarks of the PC/104 Embedded Consortium. Information regarding the traditional stackable PCI bus found on in the PC/104-Plus and PCI-104 specifications is the property of the PC/104 Embedded Consortium. All other trademarks are the property of their respective companies.

## **REVISION HISTORY**

Revision History is for this document. The initial draft Version 0.1 was written by Fastwel.

- Dec 12, 2011 StackPC Specification draft Version 0.1 released by Fastwel for internal use only.

- Feb 02, 2012

StackPC Specification draft Version 0.2 released by Fastwel for internal use only.

Changed 2.2 Pin Assignment, added Universal Types pin-outs for reference.

Changed section B.2.

Tables renumbered.

Added Figure 8-21.

Figures renumbered.

March 07, 2012 StackPC Specification draft Version 0.3 released by Fastwel for internal use only.

Changed sections 2.2 Pin Assignment, B.2.

Changed Figures 6-3, 6-4.

April 2, 2012 StackPC Specification Version 1.0 released by Fastwel.

Changed document structure.

Changed section B.2.

Tables renumbered.

Figures renumbered.

April 16, 2012 StackPC Specification Version 1.01 released by Fastwel.

Connector A pin 45 (DIR) description is clarified.

Changed Tables 2-1 (DIR added), 2-2 (STK0 resistor value, number of GND pins are changed).

Changed Tables 8-5, 8-6, 8-7 (DIR and Host ground pins added).

Changed Section 2.3 (more explanation on pass through and ground pins).

Changed Section B.3.5.

May 8, 2012 StackPC Specification Version 1.02 released by Fastwel.

One useless paragraph is removed from Section B.3.5

July 24, 2012 StackPC Specification Version 1.03 released by Fastwel.

Defined values and voltage level for STK[0:1] and Type\_DETECT# pull-up resistors, section 2.3,

page 27.

Defined values and voltage level for Config\_Type[0:2] pull-up resistors, section 4.3, page 32.

Changed figure 8-26, page 61.

October 1, 2012 StackPC Specification Version 1.04 released by Fastwel.

Changed figure 8-26, page 61.

Added figure 8-27, page 62.

April 29, 2013 StackPC Specification Version 1.1 released by Fastwel.

Removed StackPC form-factor board outline dimensions.

Added StackPC connectors layout and dimensions.

July 14, 2014 StackPC Specification Version 1.2 released by Fastwel.

Defined FBUS signal assignment in Table 2-1 and Table 2-2.

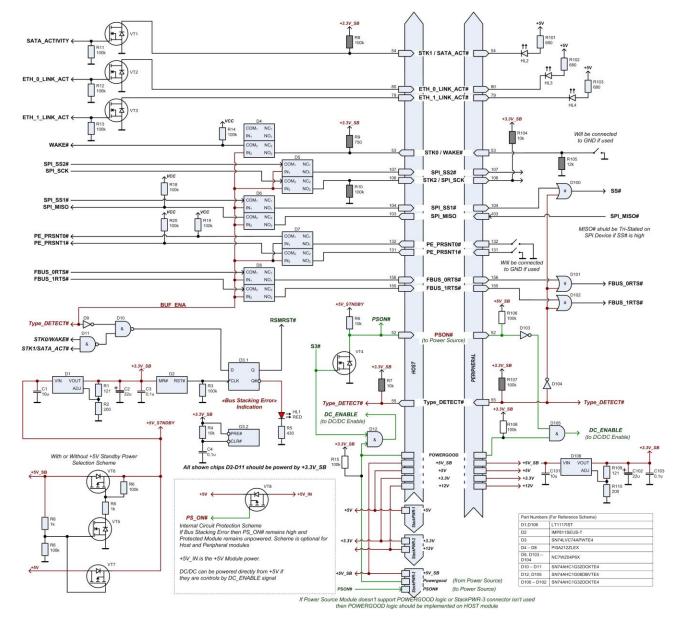

Modified Figure 8-22: Reference schematic for StackPC modules with STK protection

mechanism.

Added mounting holes on Figure 8-11.

Corrected FPE connector layout on Figure 8-30, Figure 8-32, Figure 8-34, Figure 8-37.

All pages are renumbered and font changed to Arial Unicode MS.

## TABLE OF CONTENTS

| IMPORTANT INFORMATION AND DISCLAIMERS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| TRADEMARKS AND COPYRIGHTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2                                                                                            |

| REVISION HISTORY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3                                                                                            |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5                                                                                            |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                            |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10                                                                                           |

| GLOSSARY OF TERMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 11                                                                                           |

| <ol> <li>INTRODUCTION</li> <li>Purpose</li> <li>Standard Identification</li> <li>Description</li> <li>Description</li> <li>Comparison to Other Standards</li> <li>StackPC typical applications</li> <li>1.5.1 Stackable embedded computers</li> <li>1.5.2 Expansion Bus for Single board Computers</li> <li>1.5.3 Computer-On-Module for mounting on carrier board</li> <li>StackPC signals groups descriptions</li> <li>1.6.1 PCI Express Expansion Bus</li> <li>1.6.2 Express Card Interface</li> <li>1.6.3 PCI Expansion Bus</li> <li>1.6.4 System Clocking</li> <li>1.6.5 Universal Serial Bus</li> <li>1.6.6 Serial ATA Interface</li> <li>1.6.7 Gigabit Ethernet</li> </ol> | 12<br>13<br>14<br>16<br>18<br>18<br>18<br>19<br>20<br>21<br>21<br>21<br>22<br>22<br>22<br>22 |

| <ul> <li>1.6.8 Low Pin Count Interface</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23<br>23<br>23<br>24<br>25<br>25<br>25<br>25<br>25<br>26<br>26                               |

| 1.6.13.3       +5V StandBy (+5V_SB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 26<br>27                                                                                     |

|    | 1.7.        | References                                                                    |    |

|----|-------------|-------------------------------------------------------------------------------|----|

|    | 1.8.        | Signal Naming Convention                                                      | 29 |

|    |             |                                                                               |    |

| 2. | EXPAN       | NSION CONNECTOR A (StackPC)                                                   |    |

|    | 2.1.        | Functions                                                                     |    |

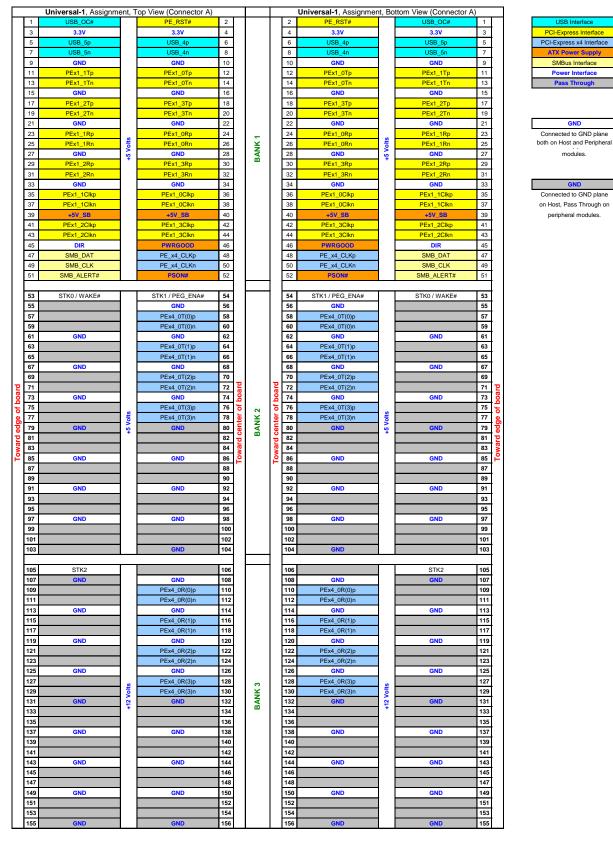

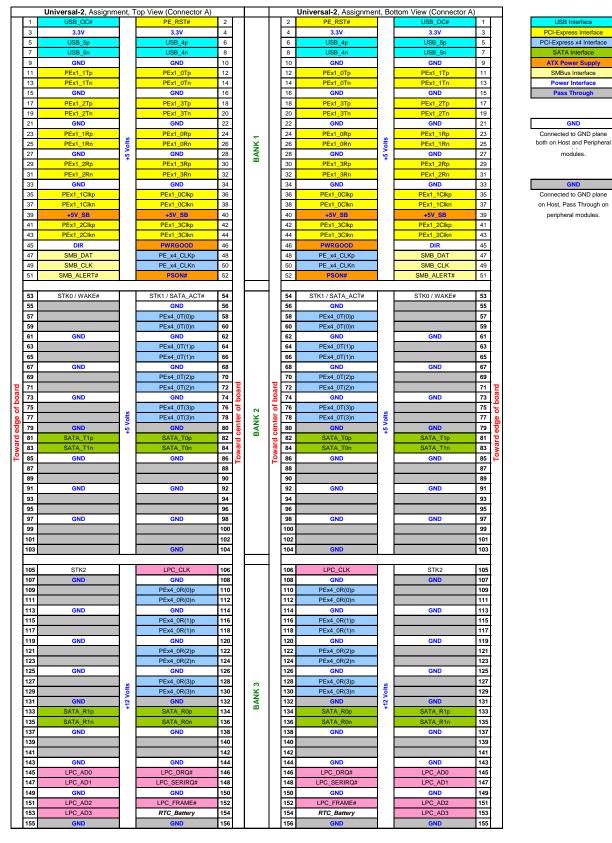

|    | 2.2.        | Pin Assignment                                                                |    |

|    | 2.3.        | Signal Descriptions                                                           |    |

|    |             |                                                                               |    |

| 2  | EVDAN       | NSION CONNECTOR B (PCI-104)                                                   | 25 |

| 5. | EAFAP       | NSION CONNECTOR B (FCI-104)                                                   |    |

|    |             |                                                                               |    |

| 4. |             | NSION CONNECTOR B1 (FPE)                                                      |    |

|    | 4.1.        | Functions                                                                     |    |

|    | 4.2.        | Pin Assignment                                                                |    |

|    | 4.3.        | Signal Descriptions                                                           |    |

|    |             | 4.3.1 PCI Express Links                                                       |    |

|    |             | 4.3.1.1 x16 Link Alternate Uses                                               |    |

|    |             | 4.3.1.2 x8 and x4 Links<br>4.3.1 FPE Bus Stacking Error (FPE_Bus_Err#) Signal |    |

|    |             | 4.3.1 FFE bus Stacking Ellor (FFE_bus_Ell#) Signal                            |    |

|    |             |                                                                               |    |

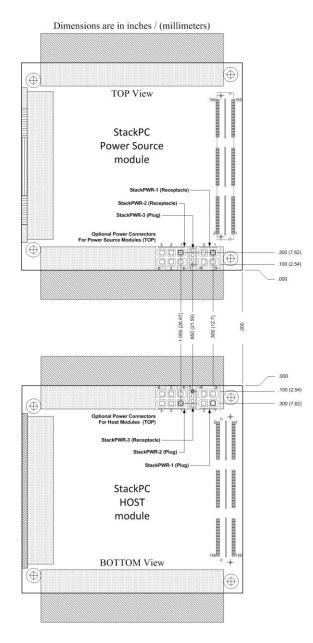

| 5. |             | ONAL StackPC POWER CONNECTORS (StackPWR)                                      |    |

|    | 5.1.        | Functions                                                                     |    |

|    | 5.2.        | Pin Assignment                                                                |    |

|    | 5.3.        | Mounting Options                                                              | 40 |

|    |             |                                                                               |    |

| 6. |             | KING                                                                          |    |

|    |             | Host and Peripheral Modules relative position in the Stack                    |    |

|    | 6.2.        | StackPC Stack-Up Link Shifting                                                |    |

|    |             | 6.2.1 PCB Link Shifting                                                       |    |

|    |             | 6.2.2 Link Shifting Stack Examples                                            |    |

|    | 6.3.        |                                                                               |    |

|    | 6.4.        | Stack Configuration Examples                                                  | 46 |

|    |             |                                                                               |    |

| 7. | ELECT       | TRICAL SPECIFICATION                                                          |    |

|    | 7.1.        | Power and Ground                                                              |    |

|    |             | 7.1.1 Connector A (StackPC) Power Capabilities                                |    |

|    |             | 7.1.2 Connector B1 (FPE) Power Capabilities                                   | 48 |

|    |             | 7.1.3 StackPWR Connectors Power Capabilities                                  |    |

|    | 7.2.        |                                                                               |    |

|    |             | 7.2.1 Stackable PCI Express Expansion Bus                                     |    |

|    |             | 7.2.2 Stackable PCI Expansion Bus                                             |    |

|    |             | 7.2.3 Gigabit Ethernet                                                        |    |

|    |             | 7.2.4 USB, SATA, LPC, SPI, SMBus                                              |    |

|    |             |                                                                               |    |

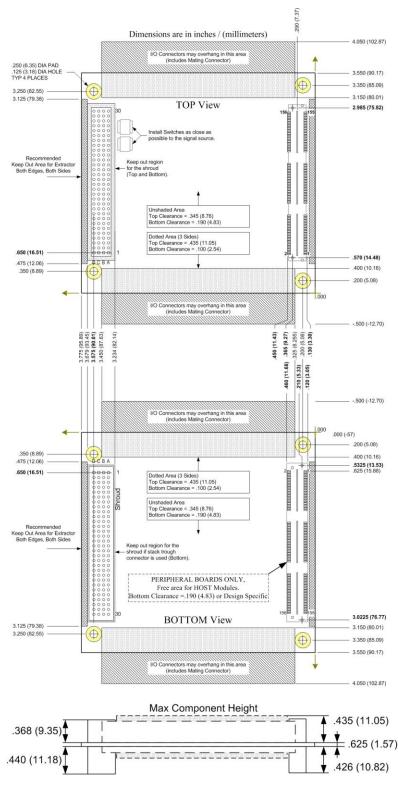

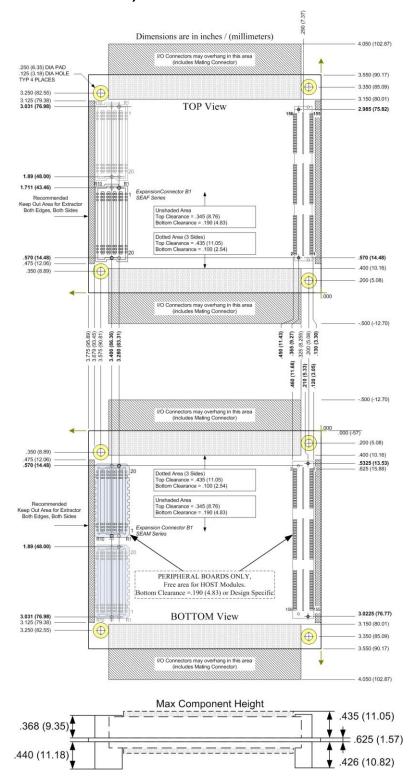

| 8. | MECH        | ANICAL SPECIFICATIONS                                                         |    |

|    | 8.1.        | Connector A (StackPC)                                                         | 51 |

|    |             | 8.1.1 Part Number                                                             |    |

|    |             | 8.1.2 Connector A (StackPC) Specifications                                    |    |

|    | 8.2.        | Connector B (PCI-104)                                                         |    |

|    | 8.3.        |                                                                               |    |

|    |             | 8.3.1 Connector B1 (FPE) Part Number                                          |    |

|    | 0.4         | 8.3.2 Connector B1 (FPE) Specifications                                       |    |

|    | 8.4.<br>8.5 | StackPC Power Connectors (StackPWR)                                           |    |

|    | 8.5.        | Standoffs                                                                     |    |

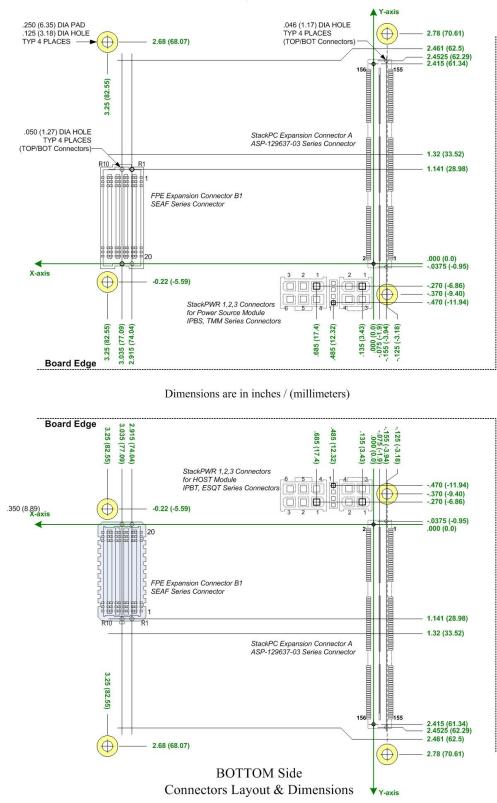

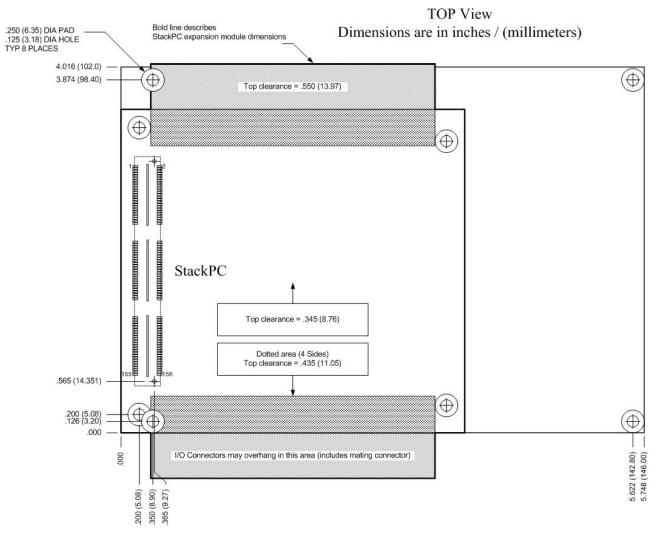

| 8.6. Stac   | kPC Layout & Dimensions                                                            | 57 |

|-------------|------------------------------------------------------------------------------------|----|

| APPENDIX A: | Layout and Routing Recommendations                                                 | 59 |

|             | A.1 Routing Topology                                                               |    |

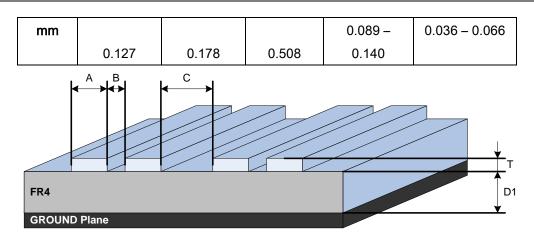

|             | A.2 Microstrip Example                                                             |    |

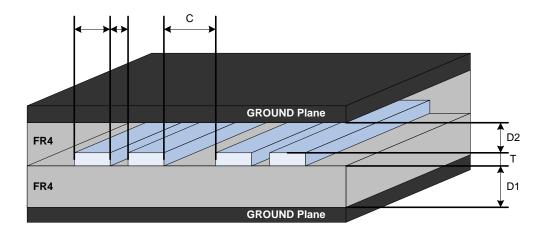

|             | A.3 Stripline Example                                                              |    |

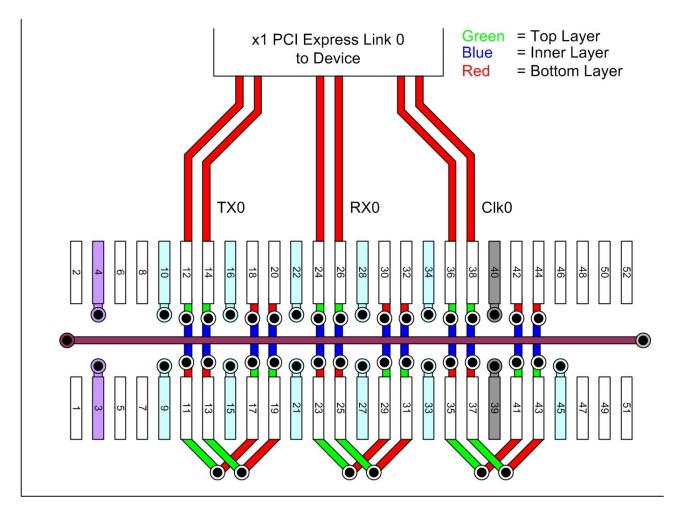

|             | A.4 Device connector Break-Out Example                                             | 64 |

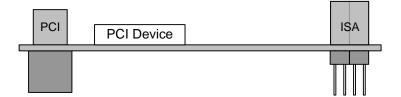

| APPENDIX B: | Compatibility with PC/104 family of standards.                                     | 65 |

|             | B.1 PC/104 (ISA)                                                                   | 65 |

|             | B.2 PCI-104 (PCI)                                                                  | 66 |

|             | B.3 PCIe/104                                                                       | 66 |

|             | B.3.1 StackPC Universal                                                            | 70 |

|             | B.3.2 StackPC Universal-1                                                          | 72 |

|             | B.3.3 StackPC Universal-2                                                          | 74 |

|             | B.3.4 Full Featured StackPC                                                        | 76 |

|             | B.3.5 PCIe/104 design recommendations to support StackPC modules                   | 77 |

|             | B.3.6 Interfaces compatibility summary                                             | 78 |

|             | B.3.7 Stack-Up and Stack-Down configurations                                       | 80 |

|             | B.3.8 x16 PCIe link support                                                        |    |

|             | B.3.9 StackPC products labeling                                                    | 82 |

| APPENDIX C: | Expansion Connector B1 (FPE) Configurable Section Profiles.                        |    |

|             | C.1 FPE Profile-7 (Unused)                                                         |    |

|             | C.2 FPE Profile-0 (User Defined)                                                   |    |

|             | C.3 FPE Profile-1 (USB 3.0)                                                        | 86 |

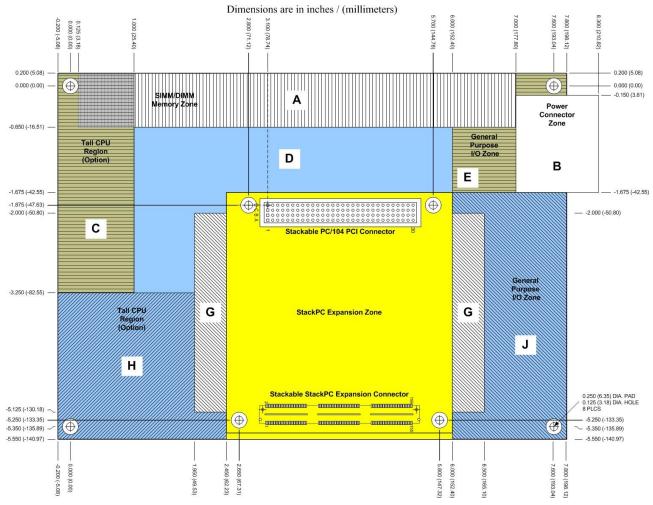

| APPENDIX D: | StackPC and StackPWR Layout & Dimensions (Adoption to PC/104 standard form-factor) | 87 |

| APPENDIX E: | StackPC-PCI Layout & Dimensions (Adoption to PC/104 standard form-factor)          | 88 |

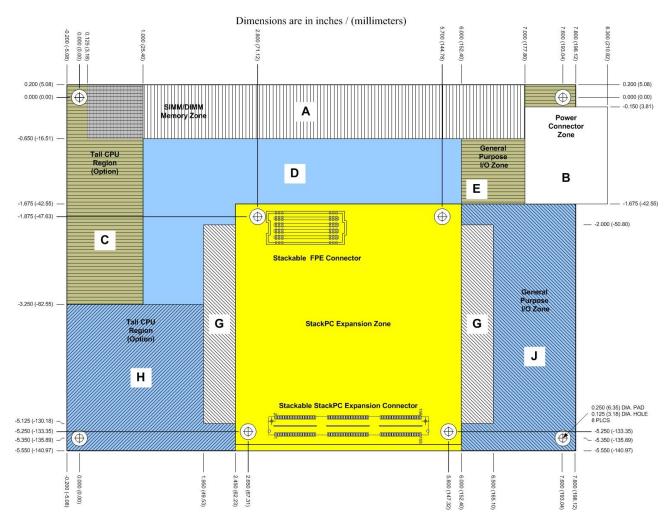

| APPENDIX F: | StackPC-FPE Layout & Dimensions (Adoption to PC/104 standard form-factor)          | 89 |

| APPENDIX G: | EPIC SBC with StackPC support (Adoption to EPIC standard form-factor)              | 90 |

| APPENDIX H: | EBX SBC with StackPC support (Adoption to EBX standard form-factor)                |    |

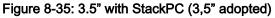

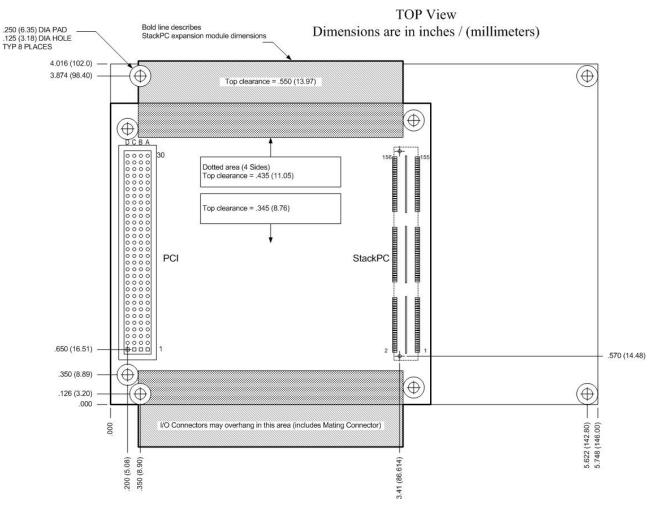

| APPENDIX I: | 3.5" SBC with StackPC support (Adoption to 3,5" standard form-factor)              | 94 |

## LIST OF FIGURES

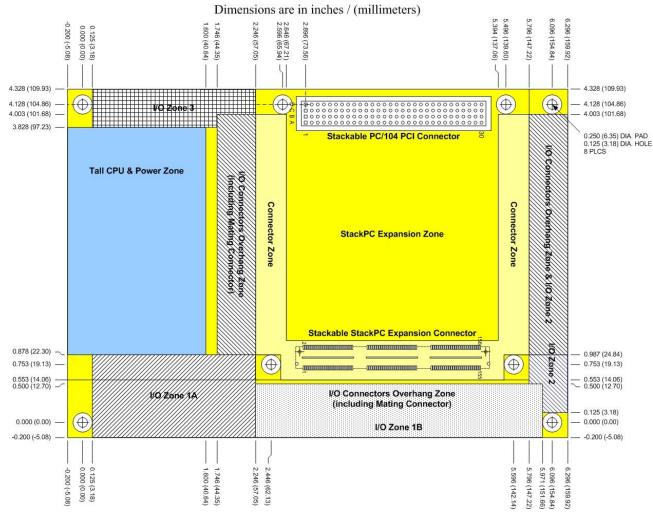

| Figure 1-1: StackPC, StackPC-FPE and StackPC-PCI general board layouts                          | 15 |

|-------------------------------------------------------------------------------------------------|----|

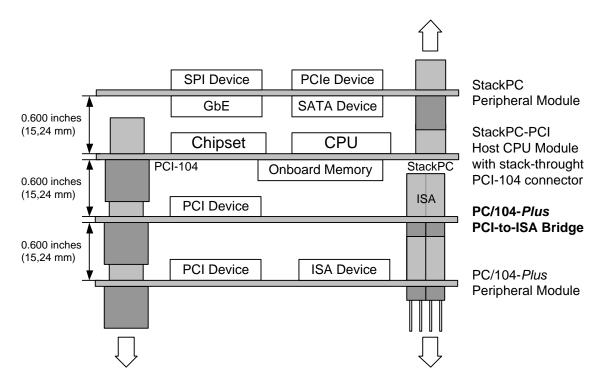

| Figure 1-2: StackPC embedded system example                                                     | 19 |

| Figure 1-3: SBC expansion with StackPC peripheral module                                        | 20 |

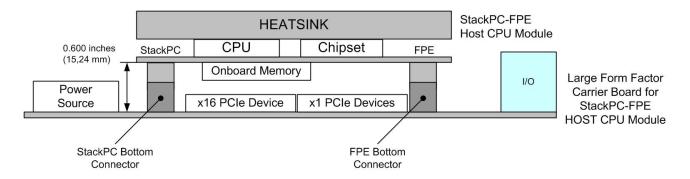

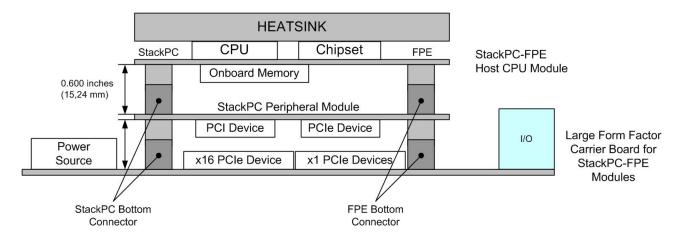

| Figure 1-4: Computer-On-Module application of StackPC-FPE CPU module.                           | 20 |

| Figure 1-5: Computer-On-Module application of StackPC-FPE CPU and Peripheral modules stack      | 21 |

| Figure 1-6: Example of using Battery power in StackPC stack.                                    |    |

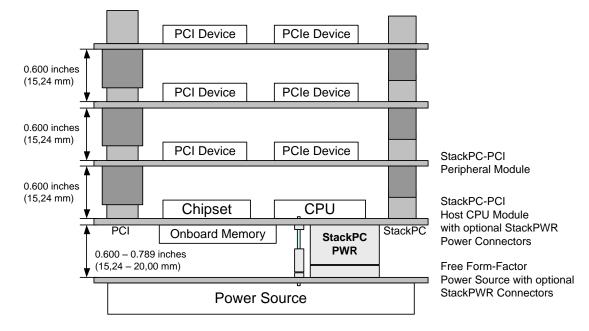

| Figure 6-1: StackPC Host Module always configured as a "bottom" module in stack                 | 42 |

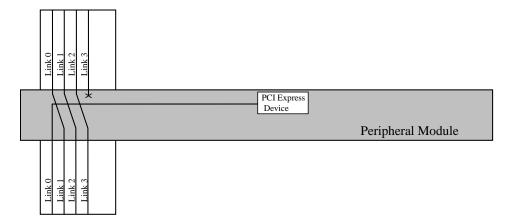

| Figure 6-2: StackPC Peripheral Module Link Shifting                                             | 43 |

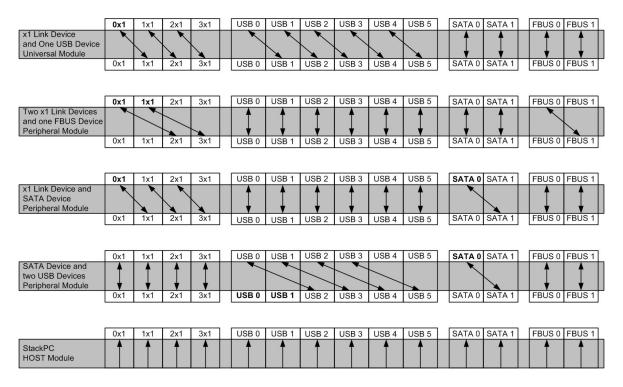

| Figure 6-3: Link Shifting Examples for Host and Various Peripheral Modules                      | 44 |

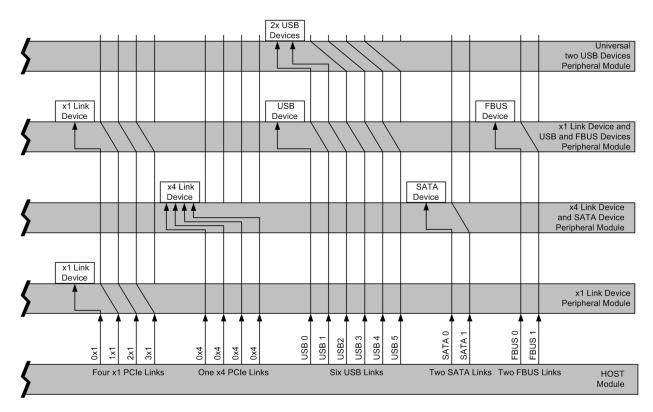

| Figure 6-4: Automatic Link Shifting Stack-Up Example with PCIe, USB, SATA and FBUS interfaces   | 45 |

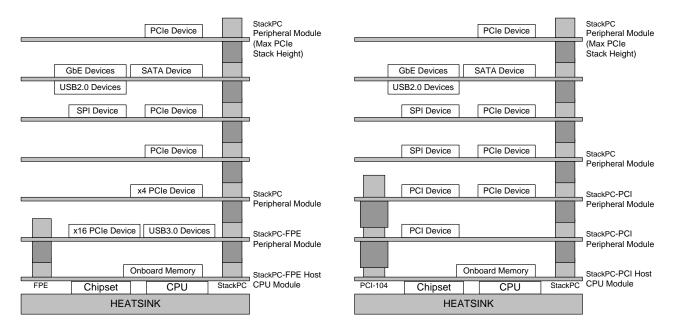

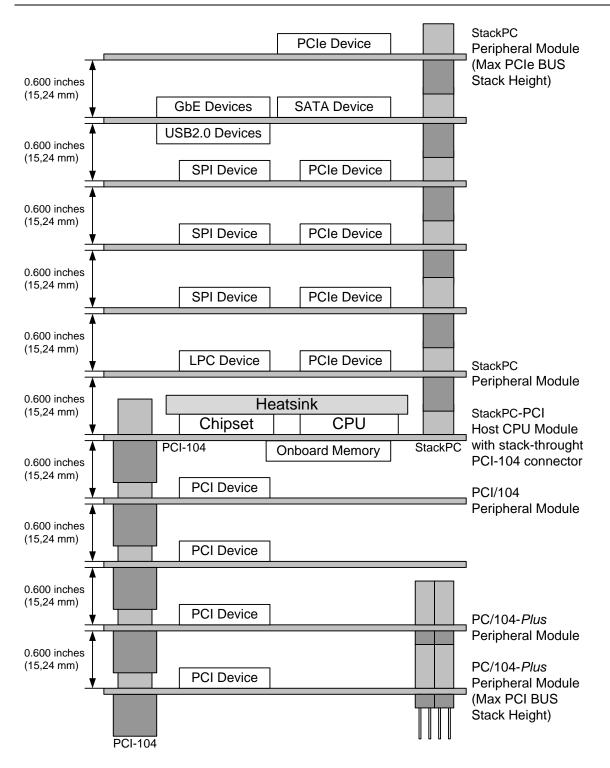

| Figure 6-5: Stack-Up Configuration Examples for StackPC-FPE and StackPC-PCI.                    | 46 |

| Figure 6-6: Stack-Up Configuration Example Using Power Module with StackPWR Connectors          | 46 |

| Figure 6-7: Combined Stack-Up and Stack-Down Configuration Example                              | 47 |

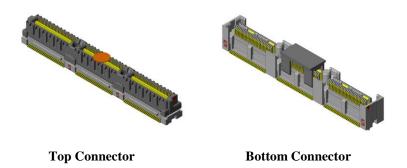

| Figure 8-1: Top Connector ASP-129637-03 or equivalent                                           | 51 |

| Figure 8-2: Bottom Connector ASP-129646-03 or equivalent                                        | 51 |

| Figure 8-3: Top Half and Bottom Half Connectors shown with Pick-and-Place Adapters              | 52 |

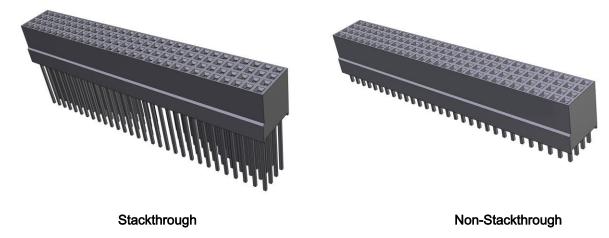

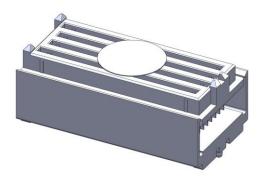

| Figure 8-4: Stackthrough and Non-Stackthrough PCI-104 connectors                                | 53 |

| Figure 8-5: Top Connector SEAF-20-06.0-X-10-2-A                                                 | 54 |

| Figure 8-6: Bottom Connector SEAM-20-09.0-X-10-2-A                                              | 54 |

| Figure 8-7: Host StackPWR Connectors                                                            |    |

| Figure 8-8: Power Module StackPWR Connectors                                                    | 56 |

| Figure 8-9: Power Source StackPWR-1 and StackPWR-2 Cable connectors                             |    |

| Figure 8-10: Standoff Mechanical Dimensions                                                     | 57 |

| Figure 8-11: StackPC Layout & Dimensions                                                        |    |

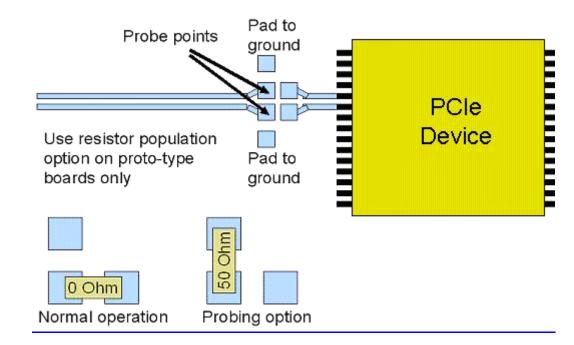

| Figure 8-12: Test point and probing for PCIe link                                               | 60 |

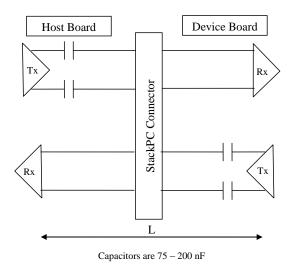

| Figure 8-13: Capacitor placement                                                                | 61 |

| Figure 8-14: MicroStrip example                                                                 | 62 |

| Figure 8-15: Stripline example                                                                  | 63 |

| Figure 8-16: Example for break-out routing of connector Bank 1 from bottom to top with shifting | 64 |

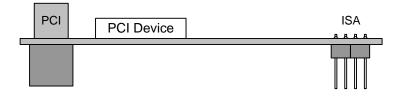

| Figure 8-17: Basic configuration of the PCI-to-ISA Bridge module (PC/104-Plus)                  | 65 |

| Figure 8-18: Stack-Down configuration of the PCI-to-ISA Bridge module                           | 65 |

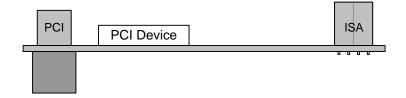

| Figure 8-19: Stack-Up configuration of the PCI-to-ISA Bridge module                             | 66 |

| Figure 8-20: Using Basic version of PCI-to-ISA Bridge module with StackPC-PCI Host              | 66 |

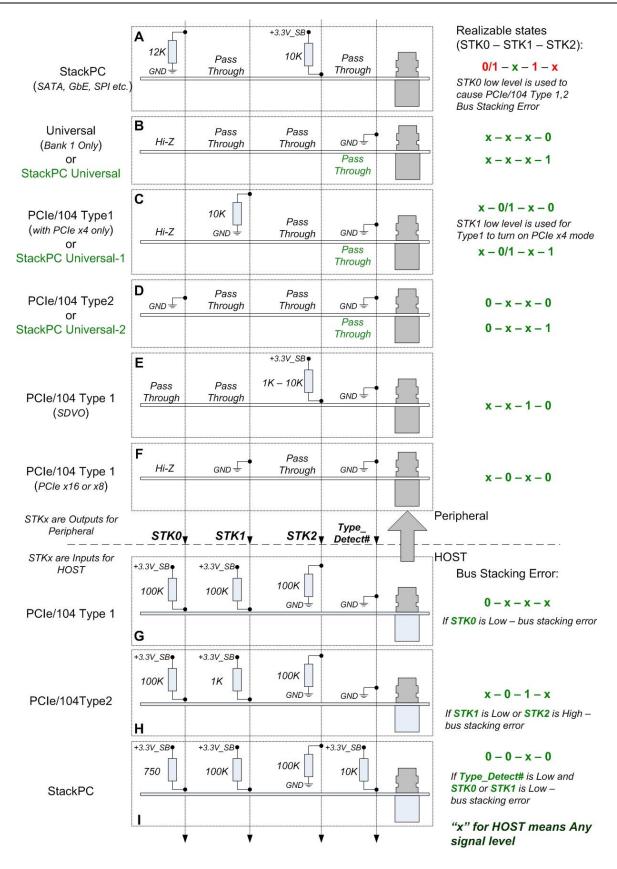

| Figure 8-21: STK protection mechanism for StackPC and PCIe/104 Type 1 and Type 2 modules        | 68 |

| Figure 8-22: Reference schematic for StackPC modules with STK protection mechanism              | 69 |

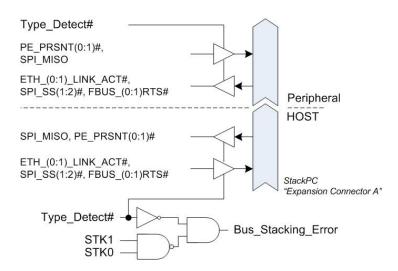

| Figure 8-23: Bus Stacking Error and Type_DETECT# logic for full featured StackPC Host and peripher | als77 |

|----------------------------------------------------------------------------------------------------|-------|

| Figure 8-24: StackPC-PCI Host module with optional PCI/104-Express Support                         | 80    |

| Figure 8-25: StackPC-PCI Host module with StackPC modules on Top and PCI/104-Express module of     | n     |

| Bottom                                                                                             | 81    |

| Figure 8-26: «StackPC-FPE to PCIe/104» bridge module                                               | 81    |

| Figure 8-27: Stack using «StackPC-FPE to PCIe/104» bridge module                                   | 82    |

| Figure 8-28: StackPWR connectors location for StackPC module (PC/104 adopted)                      | 87    |

| Figure 8-29: StackPC-PCI Module Dimensions (PC/104 adopted)                                        | 88    |

| Figure 8-30: StackPC-FPE Module Dimensions (PC/104 adopted)                                        | 89    |

| Figure 8-31: EPIC with StackPC-PCI (EPIC adopted)                                                  | 90    |

| Figure 8-32: EPIC with StackPC-FPE (EPIC adopted)                                                  | 91    |

| Figure 8-33: EBX with StackPC-PCI (EBX adopted)                                                    | 92    |

| Figure 8-34: EBX with StackPC-FPE (EBX adopted)                                                    | 93    |

| Figure 8-35: 3.5" with StackPC (3,5" adopted)                                                      | 94    |

| Figure 8-36: 3.5" with StackPC-PCI (3,5" adopted)                                                  | 95    |

| Figure 8-37: 3.5" with StackPC-FPE (3,5" adopted)                                                  | 96    |

## LIST OF TABLES

| Table 1-1: Comparison of Different Form Factors             | 17 |

|-------------------------------------------------------------|----|

| Table 1-2: References                                       | 29 |

| Table 2-1: StackPC Connector A Pin Assignments              | 32 |

| Table 2-2: Connector A (StackPC) Signals                    |    |

| Table 4-1: Connector B1 (FPE) Pin assignments               | 36 |

| Table 4-2: Connector B1 (FPE) Signals                       | 37 |

| Table 4-3: x16 Link as Two x8 or Two x4 Links               |    |

| Table 5-1: StackPWR connectors pinout                       | 40 |

| Table 7-1: Connector A (StackPC) Power Delivery             | 48 |

| Table 7-2: Connector B1 (FPE) Power Delivery                | 48 |

| Table 7-3: StackPWR Connectors Power Delivery.              | 49 |

| Table 8-1: Via and Trace length budget                      | 60 |

| Table 8-2: PCI Express routing specification                | 61 |

| Table 8-3: Typical Trace dimensions for microstrip with FR4 | 61 |

| Table 8-4: Typical Trace dimensions for stripline with FR4  | 63 |

| Table 8-5: Universal Connector A Pin Assignments            | 71 |

| Table 8-6: Universal-1 Connector A Pin Assignments          | 73 |

| Table 8-7: Universal-2 Connector A Pin Assignments          | 75 |

| Table 8-8: StackPC and PCIe/104 Compatibility table         | 79 |

| Table 8-9: Connector B1 (FPE) Profile-7 Pin assignments     | 84 |

| Table 8-10: Connector B1 (FPE) Profile-0 Pin assignments    | 85 |

| Table 8-11: Connector B1 (FPE) Profile-1 Pin assignments    | 86 |

## **GLOSSARY OF TERMS**

| Terms         | Definitions                                                                                |

|---------------|--------------------------------------------------------------------------------------------|

| ATX           | Advanced Technology Extended                                                               |

|               | A specification for PC motherboards, power supplies, and system chassis. One of its        |

|               | most notable features is support for "Standby" and "Soft-Off" power savings modes.         |

| StackPC       | StackPC specifications. Refers also to boards containing only Basic "Expansion             |

|               | Connector A" (StackPC connector).                                                          |

| StackPC-PCI   | Refers to boards containing Basic "Expansion Connector A" (StackPC connector) and          |

|               | "Expansion Connector B" with parallel PCI-bus (PCI-104 connector).                         |

| StackPC-FPE   | Refers to boards containing Basic "Expansion Connector A" (StackPC connector) and          |

|               | "Expansion Connector B1" (FPE connector).                                                  |

| PCI-104       | "Expansion Connector B" with parallel PCI bus. Refers also to PCI/104 form factor          |

|               | having mechanically and electrically compatible PCI bus connector.                         |

| FPE           | "Fat Pipe Expansion" - optional high speed "Expansion Connector B1".                       |

| Device        | A logical device attached to a PCIe Link. Generally an add-in card.                        |

| EBX           | Form factor for SBC's                                                                      |

| Host          | The central connection of a PCIe system, typically a CPU module. This is called the        |

|               | "Root Complex" by the PCIe specification.                                                  |

| Lane          | Fundamental unit of a PCI Express connection. A set of differential signal pairs, one      |

|               | pair for transmission, and one pair for reception. Multiple lanes may be combined to       |

|               | increase bandwidth (up to x16). A "by-N Link" is comprised of N Lanes.                     |

| Link          | The collection of one or more PCI Express Lanes, plus an additional differential pair for  |

|               | a clock, which make up a standard PCI Express interconnect. According to PCI               |

|               | Express Specification 1.1 a Link can be comprised of 1, 4, 8, or 16 Lanes.                 |

| Packet Switch | A device used to attach multiple PCIe devices to a single link on the HOST. The PCIe       |

|               | Specification refers to this simply as a "Switch." In this document, the term "Packet      |

|               | Switch" is used to differentiate from a "Signal Switch."                                   |

| PCle          | PCI Express                                                                                |

| SBC           | Single Board Computer                                                                      |

| Signal Switch | An analog switch used to select between multiple PCIe devices to attach to a single        |

|               | PCIe link, or multiple links to attach to a single device. Also called a "Channel Switch." |

## 1. INTRODUCTION

#### 1.1. Purpose

This document defines a new standard for stackable modular industrial computers based on modern serial interconnects for data exchange between modules such as PCI Express with x1, x4, x8 and x16 links, SATA, USB and Gigabit Ethernet. The standard gives an opportunity to use low bandwidth interconnects such as LPC, SPI and others for expansion of host computing boards with peripheral modules.

The purpose of this Specification is to provide a System level Stack-Up Only approach. Specification adopts PCI-Express, Ethernet, SATA, USB as well as LPC, SPI, Field Buses and Common Power Connector to the any stacked architecture.

StackPC Specification defines StackPC, FPE, StackPWR connectors relative position and stacked systems organization common approach. Also specification describes using stack modules in COM applications.

Specification is targeted not only for traditional stackable systems with all boards of the same form factor, but also for other stackable architectures like COM applications (mezzanine Computer-On-Module in conjunction with base board) and SBC expansion (expansion bus for Single Board Computers of various form factors).

PCI Express was chosen because of its performance, scalability and wide market acceptance.

Ethernet was chosen as the most popular long distance data interconnect, which is inevitable in modern computer based environments.

SATA was chosen as the storage interconnect because of wide acceptance and bandwidth scalability.

LPC bus, SPI and other signaling interfaces were chosen because of their capabilities to provide support for legacy devices and to expand host processor functionality in simple and cost effective way.

Additionally specification describes adoption StackPC to popular standards such as PC/104, 3.5 inch, EPIC and EBX. This adoption is as result of StackPC and PCIe/104 compatibility with Bank1 signals (same connector and similar pinout).

## 1.2. Standard Identification

This standard defines three versions of modules that are mechanically and electrically compatible with each other, but differ in a set of supported interfaces:

StackPC. This version has one StackPC expansion connector. The following interfaces are supported:

| 4x1 PCle<br>1x4 PCle<br>USB 2.0 | <ul> <li>4 root ports, 4 clocks</li> <li>1 root port, 1 clock</li> <li>6 ports</li> </ul> |

|---------------------------------|-------------------------------------------------------------------------------------------|

| SATA                            | – 2 ports                                                                                 |

| Gigabit Ethernet<br>LPC         | – 2 ports                                                                                 |

| FBUS                            | – 2 ports                                                                                 |

| SPI, SMB                        |                                                                                           |

StackPC-PCI. This version has two expansion connectors – StackPC and PCI-104. The following interfaces are supported:

| 4x1 PCle         | – 4 root ports, 4 clocks                                    |

|------------------|-------------------------------------------------------------|

| 1x4 PCle         | – 1 root port, 1 clock                                      |

| PCI              | – 32-bit, 33 MHz, support for up to four PCI-master devices |

| USB 2.0          | – 6 ports                                                   |

| SATA             | - 2 ports                                                   |

| Gigabit Ethernet | – 2 ports                                                   |

| LPC              |                                                             |

| FBUS             | – 2 ports                                                   |

| SPI, SMB         |                                                             |

StackPC-FPE. This version has two expansion connectors – StackPC and FPE (Fat Pipe Expansion). The following interfaces are supported:

| 4x1 PCle<br>1x4 PCle<br>1x16/2x8/2x4 PCle<br>USB 2.0/3.0<br>SATA<br>Gigabit Ethernet<br>Display Port<br>LPC | <ul> <li>4 root ports, 4 clocks</li> <li>1 root port, 1 clock</li> <li>2 root ports, 2 clocks</li> <li>6 ports</li> <li>2 ports</li> <li>2 ports</li> <li>1 port</li> </ul> |

|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FBUS<br>SPI, SMB<br>Configurable Section                                                                    | – 2 ports                                                                                                                                                                   |

## 1.3. Description

StackPC specification is designed to deal with challenges caused by modern point-to-point high speed serial interfaces to stackable architecture which used to rely on traditional parallel bus interfaces. New specification is suitable for using for SBC expansion and fully opens Computer On Module like area of applications. It also paves the way for using even higher speed interfaces which are just emerging on embedded arena.

Compared to past years systems, modern embedded solutions require support for greater number of input/output interfaces. With each year, new processor modules support more and more input/output interfaces integrated in system logic. This makes necessary to place additional interface connectors on processor and peripheral modules. Compactness of Small Form Factor modules is an impediment to placement of necessary components and sufficient number of input/output connectors. It should be noted, that stackable modules are mostly designed for harsh environments and require installation inside an enclosure to protect them from mechanical impact or corrosive substances. Hence, embedded systems manufacturers have to resort to various tricks to bring out all interfaces to connectors on the front panel of enclosure using flat cables.

One of the solutions can be to aggregate the main set of input/output interfaces at the stack connectors. This allows to avoid some interface connectors (usually pin headers) and to provide more space on the module for placement of necessary components. This, in turn, leads to reduction of manufacturing cost and adds flexibility in terms of using the module in applications requiring limited functionality. Reducing cabling inside the enclosure improves convection, reduces magnetic noise pickup, and consequently, increases system effectiveness. Interfaces aggregated at the stack connectors can be led out of the enclosure using inexpensive and efficient solution – terminal interface module carrying the necessary set of standard interface connectors.

One of rather important requirements to the new specification is compatibility with family of PC/104 standards. The support for existing and field proven PC/104, PC/104-Plus, PCI/104, PCIe/104 and PCI/104-Express modules is provided. Details about compatibility between StackPC and PC/104 standards can be found in Appendix B.

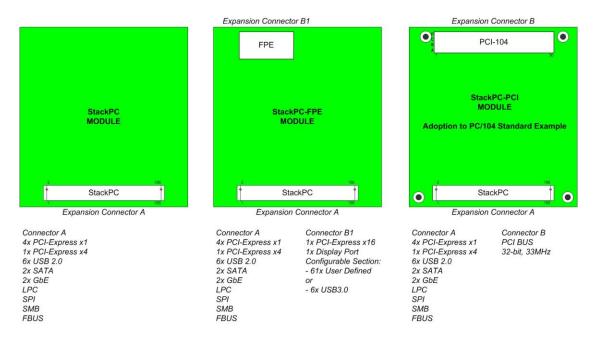

StackPC specification defines following versions of modules:

**1. StackPC.** Only StackPC connector is mounted onboard to provide support for most popular high-speed and legacy interfaces. Four x1 and one x4 PCI Express links are supported simultaneously as well as USB 2.0 interfaces, Gigabit Ethernet, SATA and others. Modules in this form factor use basic set of interfaces which are required in most embedded applications.

**2. StackPC-PCI.** Two connectors are mounted onboard – StackPC and PCI-104. Modules in this form factor provide basic set of modern interfaces plus compatibility with still widely used modules having parallel PCI bus.

**3. StackPC-FPE.** In addition to basic StackPC connector an optional FPE (Fat Pipe Expansion) connector is used. This optional FPE connector brings extra 1x16 or 2x8 (x4, x1) PCI Express lanes, Display port and Configurable Section of signals in addition to basic set of StackPC interfaces. StackPC-FPE modules can be used for high performance and multimedia systems.

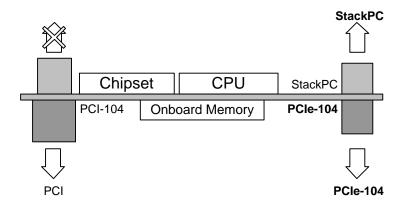

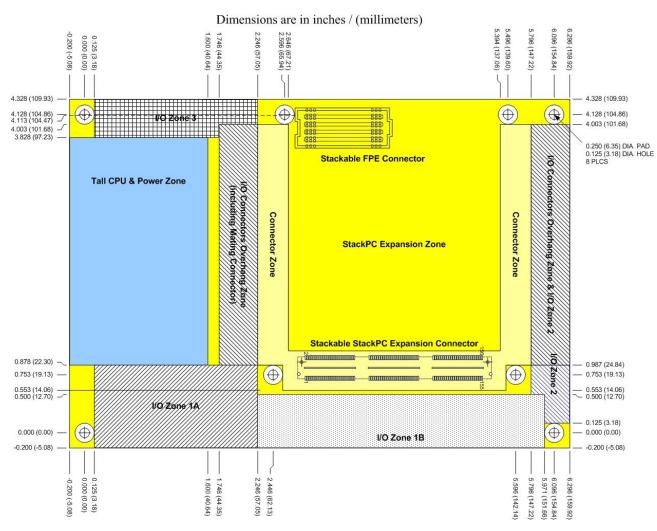

Figure 1-1 shows a basic view of StackPC layouts.

Figure 1-1: StackPC, StackPC-FPE and StackPC-PCI general board layouts

StackPC specification defines only <u>one direction for modules stacking</u>. Following that definition, StackPC peripheral modules are stacked on top side of Host board ("Stack-Up only" configuration). This allows Host module to be more functional and more cost efficient. Host module may be on top or bottom of system stack depending from the whole system stack orientation. CPU chip can be on top or bottom of Host module depending from chosen heat dissipation approach.

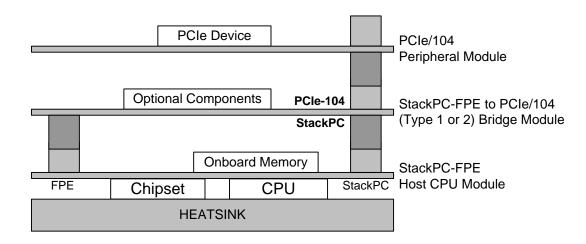

StackPC specification doesn't limit vendors on how they use Bottom side of Host module. To adopt StackPC module to PC/104 family standards additional PCIe-104 (Type 1 or Type 2) connector can be used on Bottom side providing Stack-Down configuration option or PCI-104 connector can be placed instead of FPE connector (see Figure 8-24). Depending on type of used PCIe-104 or PCI-104 connectors StackPC-PCI Host module may allow both Stack-Up and Stack-Down configurations for PCI/104 peripheral modules.

StackPC has following features:

| Connector A:                                             |                                            |  |  |  |  |  |  |

|----------------------------------------------------------|--------------------------------------------|--|--|--|--|--|--|

| 4x1 PCle                                                 | <ul> <li>4 root ports, 4 clocks</li> </ul> |  |  |  |  |  |  |

| 1x4 PCle                                                 | – 1 root port, 1 clock                     |  |  |  |  |  |  |

| USB 2.0                                                  | – 6 ports                                  |  |  |  |  |  |  |

| SATA                                                     | – 2 ports                                  |  |  |  |  |  |  |

| Gigabit Ethernet                                         | – 2 ports                                  |  |  |  |  |  |  |

| LPC                                                      |                                            |  |  |  |  |  |  |

| FBUS                                                     | – 2 ports                                  |  |  |  |  |  |  |

| SPI                                                      | – 3 slaves                                 |  |  |  |  |  |  |

| SMB                                                      |                                            |  |  |  |  |  |  |

| ATX power and control signals: +5V_SB, PS_ON#, POWERGOOD |                                            |  |  |  |  |  |  |

| Power: +3.3V, +5V, +1                                    | 12V                                        |  |  |  |  |  |  |

StackPC-PCI has the following features:

Connector A: The same as in StackPC Connector B: PCI Bus. Supports up to four 32 bit, 33 MHz PCI Bus cards each capable of Bus Mastering (same as on PC/104-Plus and PCI-104), +3.3V PCI signaling level Power: +3.3V, +5V, +12V, -12V

StackPC-FPE has the following features:

Connector A: The same as in StackPCConnector B1:1x16 PCle or 2x8 PCle or 2x4 PCleDisplay PortConfigurable SectionPower: +3.3V, +5V, +12V

## 1.4. Comparison to Other Standards

Table 1-1 presents comparison of different form factors by supported interfaces. Same color marks interfaces whose connectors are mechanically and electrically compatible, i.e. modules can be stacked without any intermediate adapter modules.

|                     | ISA | PCI        | x1<br>PCle         | x4<br>PCle         | x16 PCle                                 | USB<br>2.0 | USB<br>3.0 | SATA | GbE | LPC | SPI | SMB | User<br>I/O | Other                                              | Power                                                       |

|---------------------|-----|------------|--------------------|--------------------|------------------------------------------|------------|------------|------|-----|-----|-----|-----|-------------|----------------------------------------------------|-------------------------------------------------------------|

| PC/104              | 1   |            |                    |                    |                                          |            |            |      |     |     |     |     |             |                                                    | +5V, -5V,<br>+12V, -12V                                     |

| PC/104-Plus         | 1   | 4<br>slots |                    |                    |                                          |            |            |      |     |     |     |     |             |                                                    | +5V, -5V,<br>+12V, -12V                                     |

| PCI/104             |     | 4<br>slots |                    |                    |                                          |            |            |      |     |     |     |     |             |                                                    | +3.3V, +5V,<br>+5V_SB, +12V                                 |

| PCIe/104<br>Type 1  |     |            | 4<br>root<br>ports |                    | 1 x16 or<br>2 x8 or<br>2 x4 or<br>2 SDVO | 2          |            |      |     |     |     | 1   |             |                                                    | +3.3V, +5V,<br>+5V_SB, +12V                                 |

| PCIe/104<br>Type 2  |     |            | 4<br>root<br>ports | 2<br>root<br>ports |                                          | 2          | 2          | 2    |     | 1   |     | 1   |             |                                                    | +3.3V, +5V,<br>+5V_SB,<br>+12V,<br>RTC_Battery              |

| PCI/104-<br>Express |     | 4<br>slots | 4<br>root<br>ports |                    | 1 x16 or<br>2 x8 or<br>2 x4 or<br>2 SDVO | 2          |            |      |     |     |     | 1   |             |                                                    | +3.3V, +5V,<br>+5V_SB,<br>+12V, -12V                        |

| StackPC             |     |            | 4<br>root<br>ports | 1<br>root<br>port  |                                          | 6          |            | 2    | 2   | 1   | 3   | 1   |             | 2x FBUS,<br>2 Express<br>Cards                     | +3.3V, +5V,<br>+5V_SB,<br>+12V,<br>RTC_Battery              |

| StackPC-PCI         |     | 4<br>slots | 4<br>root<br>ports | 1<br>root<br>port  |                                          | 6          |            | 2    | 2   | 1   | 3   | 1   |             | 2x FBUS,<br>2 Express<br>Cards                     | +3.3V, +5V,<br>+5V_SB,<br>+12V, -12V,<br>RTC_Battery        |

| StackPC-FPE         |     |            | 4<br>root<br>ports | root               | 1 x16 or<br>2 x8 or<br>2 x4              | 6          |            | 2    | 2   | 1   | 3   | 1   | 50          | 2x FBUS,<br>2 Express<br>Cards,<br>DisplayPor<br>t | +3.3V, +5V,<br>+5V_SB,<br>+12V,<br>RTC_Battery              |

| SUMIT A             |     |            | 1<br>root<br>port  |                    |                                          | 4          |            |      |     | 1   | 2   | 1   |             |                                                    | +3.3V, +5V,<br>+5V_SB, +12V                                 |

| SUMIT B             |     |            | 1<br>root<br>port  | 1 x4<br>or<br>2 x1 |                                          |            |            |      |     |     |     |     |             |                                                    | +3.3V, +5V,<br>+5V_SB, +12V                                 |

| Comit               |     |            | 3<br>root<br>ports | 1 x4<br>or<br>4 x1 |                                          | 6          |            | 2    | 1   | 1   | 2   | 1   |             | VGA,<br>LVDS,<br>SDIO,<br>Audio                    | +3.3V, +5V,<br>+3.3V_SB,<br>+5V_SB,<br>RTC_Battery,<br>+12V |

The same color indicates that corresponding interfaces are directly mechanically and electrically compatible if different modules are in one stack.

## 1.5. StackPC typical applications

#### 1.5.1 Stackable embedded computers.

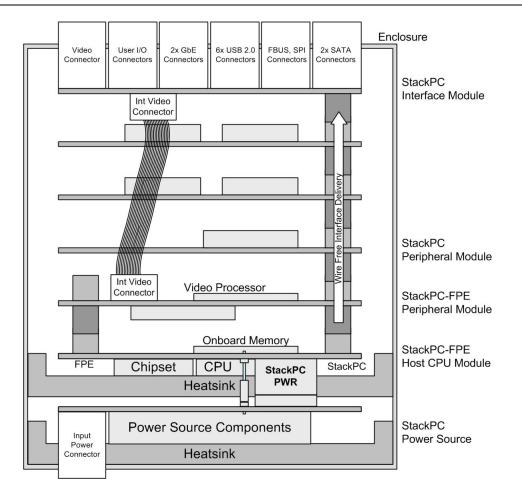

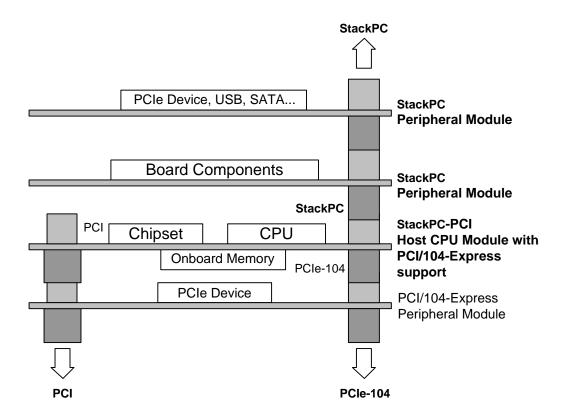

Design of rugged miniature stackable computers is traditional area of using StackPC modules. StackPC allows building complete system as a stack of CPU and various peripheral modules. Power supply module also may have the same form factor and be a part of the same stack. StackPC also defines optional power connectors that allow system designers to deliver power to the stack with unified approach.

The whole StackPC stack may have individual enclosure or be a part of complex device having additional electronics for implementing human machine interface or other application specific functions.

Currently it is not usually easy task for system designer to have all necessary interfaces to be proper connected and wired. Since StackPC standardizes propagation of most popular interfaces through main stack connectors it significantly simplifies system wiring and give a new dimension for implementing system interconnects.

Figure 1-2 shows example of StackPC system in individual enclosure. Set of high speed interfaces are delivered to I/O connectors on interface module using standard high speed StackPC connector instead of wired connections.

Figure 1-2: StackPC embedded system example

#### 1.5.2 Expansion Bus for Single board Computers

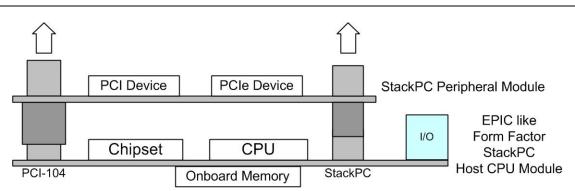

StackPC specification can be adopted as an expansion connector for single board computers (SBCs) of various standards and customer specific form factors. This specification defines how to use StackPC as an expansion bus for EBX, EPIC and 3.5" alike single board computers. StackPC can also be used as an expansion bus for SBCs of other form factors until relative locations of StackPC connectors and mounting holes are met. Figure 1-3 shows example of using StackPC peripheral board together with EPIC single board computer.

Figure 1-3: SBC expansion with StackPC peripheral module

For this kind of applications StackPC allows to expand SBC functionality with wide range of available peripheral modules. In addition to using standard PCIe lanes, StackPC peripheral modules can directly use SATA, USB 2.0, SPI, LPC, FBUS or Gigabit Ethernet interfaces available on Host SBC. It gives cost effective way of using SATA and USB storages, LPC, SPI, FBUS and Ethernet devices on peripheral modules without necessity to have PCI or PCIe interface chips or in system wiring.

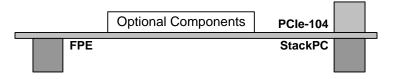

#### 1.5.3 Computer-On-Module for mounting on carrier board.

Having most popular peripheral interfaces within stack connectors StackPC opens the door to the new area of Computer-On-Module (COM) like applications which were not addressed by PC/104 family specifications. Figure 1-4 shows example of using StackPC-FPE CPU module as a Computer-On-Module mounted on application specific carrier board.

Figure 1-4: Computer-On-Module application of StackPC-FPE CPU module.

For many applications carrier board has rather tall peripheral connectors or there are no strict space limitations. In such cases it makes no sense to use low profile COM modules available on the market. Such low profile COM modules (like COM-express) put severe restrictions on height of components on COM modules and on carrier board within PCB area where COM module to be located. In practice

designers sometimes try to avoid placing any components in this area of carrier board. Using StackPC CPU module as a COM module does not apply such restrictions thus providing more flexibility and real estate for carrier board designers. Tall components can be used both on StackPC CPU module and on carrier board.

Additional unique feature of using StackPC CPU as a COM module is a possibility to add StackPC peripheral modules to the system. Figure 1-5 shows how system functionality can be extended by adding standard peripheral module between StackPC CPU and carrier board.

Figure 1-5: Computer-On-Module application of StackPC-FPE CPU and Peripheral modules stack.

## 1.6. StackPC signals groups descriptions

#### 1.6.1 PCI Express Expansion Bus

Basic StackPC connector provides four x1 PCI Express links (required) and a single x4 PCI Express link (optional). Single x4 PCI Express link can be configured as four x1 links (optional).

Optional FPE connector adds extra 1x16 Link or 2x8 Links or 2x4 PCIe Links which can be used for applications where high I/O bandwidth and/or multimedia expansion are needed.

#### 1.6.2 Express Card Interface

Low active PE\_PRSNT[0:1]# signals indicate that one or two Express Cards with PCI Express interface are presented in System. These lines are pulled up on Host. For more details, please see Express Card specification.

#### 1.6.3 PCI Expansion Bus

The PCI Expansion Bus is the same 32 bit, 33 MHz PCI bus found on the PC/104-plus and PCI-104 Specifications with the addition of +5V\_SB, PSON#, and PME#.

#### 1.6.4 System Clocking

The PCIe architecture is based on a 100 MHz reference clock. The Host may also employ spread spectrum clocking as defined in the PCI Express Base Specification to reduce EMI. In this case it is required that the Device uses the distributed clock as its reference clock. Using an on-board oscillator as a reference is not allowed.

StackPC does not define any termination on unused clock lines; therefore the Host is required to disable any unused clocks.

StackPC Host module provides four x1 and one x4 PCIe Links with separate clocks to support four x1 and one x4 PCIe Devices. StackPC-FPE has additional two clocks serving 1x16, 2x8 or 2x4 PCIe Links.

#### 1.6.5 Universal Serial Bus

Universal Serial Bus (USB) is used to connect peripherals such as storage, media, pointing devices or any other devices to the host system. This interface provides path to get and to transfer data information from the peripherals to the host system with speed up to 480 Mbps for USB 2.0.

StackPC connector supports up to 6 USB 2.0 ports. Line shifting is applicable to all USB ports as one group.

Host board provides only differential lines to the StackPC connector. Power for USB devices, should be provided by peripheral module to which they are connected.

The USB\_OC# signal is used by peripheral modules to indicate Over Current event to the Host. Any USB port in case of Over Current situation should pull low the USB\_OC# signal.

For more information, please refer to Universal Serial Bus Specifications.

#### 1.6.6 Serial ATA Interface

Serial ATA (SATA) interface is used to connect storage peripherals such as hard drives, solid state drives, optical drives, etc. and to the host system. This interface is an evolutionary replacement for the Parallel ATA physical storage interface. StackPC connector supports 2 SATA ports with link shifting.

For more information, please refer to SATA Specification.

#### 1.6.7 Gigabit Ethernet

StackPC specification defines group of two Gigabit Ethernet (GbE) ports without galvanic isolation, i.e. peripheral modules, having I/O connectors for these ports should include all necessary components for implementing physical layer, galvanic isolation, Power-Over-Ethernet, etc. Link shifting is applicable.

#### 1.6.8 Low Pin Count Interface

This interface is used for legacy I/O devices support and may be considered as ISA bus replacement for peripheral devices such as Super I/O or user FPGA. LPC interface supports I/O, Memory, DMA and Bus Master cycles while its data transfer rate is higher than ISA bus. LPC interface supports 4GB memory space.

For more information, please refer to LPC Specification.

#### 1.6.9 Field Bus Interface

Two FBUS ports can be considered as a User defined serial interfaces. It is 3.3V CMOS level serial interfaces which can be driven by UART, CAN controller, or by custom logic implementing user defined protocol. Converting CMOS levels to interface signals according particular physical layer requirements (RS-232, RS-422/485, CAN, etc), is the function of peripheral module. Peripheral modules can provide also galvanic isolation in case it is necessary. FBUS ports may be driven by Host or by Peripheral modules. In case FBUS is driven by Peripheral module this module should connect FBUS lines to Top connector only.

Each port has Rx, Tx or Positive, Negative lines and RTS# lines. Link shifting is applicable.

#### 1.6.10 Serial Peripheral Interface

The optional Serial Peripheral Interface is a four-wire interface with separate Slave Select (SS#) signal to address peripheral device. This specification defines three SS# signals to support up to three peripheral devices without any address decoding on peripheral modules.

The SPI supports Master, Slave and Bi-directional modes for communication with peripheral devices. For more information, please see SPI Block Guide from Freescale Semiconductor (see Table 1-2). SS# signals link shifting is applicable.

#### 1.6.11 System Management Bus

The optional System Management Bus (SMBus) is a two-wire interface through which various system component chips can communicate with each other and with the rest of the system. It is based on the principles of operation of I2C. SMBus provides a control bus for system and power management related tasks. A system may use SMBus to pass messages to and from devices instead of using individual control lines. Removing the individual control lines reduces pin count. Accepting messages ensures future expandability. With SMBus, a device can provide manufacturer information, tell the system what its model/part number is, save its state for a suspended event, report different types of errors, accept control parameters, and return its status. SMBus is described in System Management Bus (SMBus) Specification, Version 2.0. Refer to this specification for DC characteristics and all AC timings. If the system board or add-in card supports SMBus, it must adhere to additional requirements that can be found in Chapter 8 of the PCI Local Bus Specification, Revision. 3.0.

SMBus 2.0 Specification defines an address Resolution Protocol (ARP) that is used to assign slave addresses to SMBus devices. Although optional in the SMBus 2.0 Specification, it is required that systems that connect the SMBus to PCI slots implement ARP for assignment of SMBus slave addresses to SMBus interface devices on PCI add-in cards. The system must execute ARP on a logical SMBus whenever any PCI bus segment associated with the logical SMBus exits the B3 state or a device in an individual slot associated with the logical SMBus exits the D3 cold state. Prior to executing ARP, the system must ensure that all ARP-capable SMBus interface devices are returned to their default address state.

The system board provides pull-ups to the +3.3Vaux rail per the above specification and the components attached to these signals need to have a 3.3V signaling tolerance (5V signaling must not be used). Also, the SMBus is used during all power states, so all components attached to the SMBus must remain powered during standby, or ensure that the bus is not pulled down when not powered.

The SMBus interface is based upon the System Management Bus Specification (SMBus 2.0 Specification). This two-wire serial interface has low power and low software overhead characteristics that make it well suited for low-bandwidth system management functions.

The capabilities enabled by the SMBus interface include, but are not limited to, the following:

Support for client management technologies. Support for server management technologies. Support for thermal sensors and other instrumentation devices on StackPC modules. Peripheral modules identification when the bus is in the B3 state or when the PCI device is in the D3hot or D3cold states as defined in the PCI Power Management Interface Specification.

#### 1.6.12 Stack Control Signals

Stack control signals allow StackPC and PCIe/104 modules to define type and set of interfaces used by other modules in the same stack. That information is used to protect modules from being damaged if modules with conflicting interfaces are mixed in one stack. Detailed information on Stack Control Signals and rules can be found in Appendix B.

#### 1.6.12.1 Type\_DETECT# Signal

This signal is pulled up on StackPC Host. StackPC peripherals pass through this signal. PCIe/104 peripherals drive this signal to Low Level in case peripheral module uses interfaces which may cause conflict with StackPC specific interfaces.

#### 1.6.12.2 STK0, STK1, STK2 Signals

These signals are used for detecting interfaces conflicts between modules of different types in case they are mixed in one stack. PCIe/104 modules generate Bus Stacking Error event depending on status of STK0...2 signals. StackPC modules generate Bus Stacking Error event depending on status of STK0...2 and Type\_DETECT# signals.

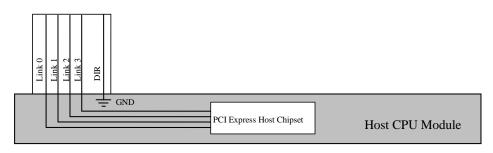

#### 1.6.12.3 Stack Direction (DIR) Signal

DIR signal is defined in PCIe/104 specification. Since StackPC specification defines only Stack-Up configuration with peripheral modules stacked only on Top of Host module, then StackPC Host module puts GND to pin 45 of Expansion A connector. Peripheral modules should pass through this signal. StackPC peripheral modules can work only on TOP of the PCIe/104 HOST module.

StackPC peripheral modules may use DIR signal to detect wrong stacking configuration. High Level on DIR signal can be used to indicate to end user that StackPC module is mistakenly stacked down.

#### 1.6.13 ATX and Power Management

StackPC incorporates all necessary control and signal lines for ATX and power management functions. These signals include PWRGOOD, PSON#, +5V\_SB, and PME#. The inclusion of these signals allows maximum power saving. All these signals are optional and all modules in one stack should work properly even if ATX and power management is not implemented.

#### 1.6.13.1 Power Good (PWRGOOD) Signal

PWRGOOD is a "power good" signal. It should be asserted high by the power supply to indicate that the +12 VDC, +5 VDC, and +3.3 VDC outputs are above the under-voltage thresholds and that sufficient main energy is stored by the converter to guarantee continuous power operation within specifications. Conversely, PWRGOOD should be de-asserted to a low state when any of the +12 VDC, +5 VDC, or +3.3 VDC output voltages falls below its under-voltage threshold, or when main-power has been removed for a sufficiently long enough time that the power supply operation cannot be guaranteed beyond the power-down warning time. If Powergood is not supported then all modules in stack should start with its own internal control.

#### 1.6.13.2 Power Supply On (PSON#) Signal

PSON# is an active-low signal that allows a CPU module to remotely control the power supply in conjunction with features such as soft on/off, Wake-on-LAN, or wake-on-modem. It is pulled up to +5V\_SB line. When PSON# is driven to Low Level, the power supply should turn on the main DC output rails: +12 VDC, +5 VDC, +3.3 VDC, -12 VDC. When PSON# is pulled to High Level or open-circuited, the DC output rails should not deliver current and should be held at zero potential with respect to ground. PSON# has no effect on the +5V\_SB output, which is always enabled whenever AC power is present.

CPU module should not drive PSON# signal Low in case Bus Stacking Error detected. PSON# signal can be used for indication that interface conflict has happened in stack.

#### 1.6.13.3 +5V StandBy (+5V\_SB)

+5V\_SB is a standby supply output that is active whenever AC power is present. It provides a power source for circuits that must remain operational when the main DC output rails are in a disabled state. Example uses include soft power control, Wake-on-LAN, wake-on-modem, intrusion detection, or suspend state activities.

+5V\_SB power is used to obtain +3.3V\_SB power to support PME# or WAKE# functionality.

#### 1.6.13.4 Power Management Event (PME#) Signal

The PME# signal is an active-low, open-drain signal that can be used by a device to request a change in the device or system power state. This signal can be shared among all devices in the system. Devices must be enabled by software before asserting this signal. Once asserted, the device must continue to drive the signal low until software explicitly clears the condition in the device.

The use of PME# is specified in the PCI Bus Power Management Interface Specification. Host and Devices using PME# must pull-up it to +3.3V\_SB. Modules that do not use PME# signal have associated pin unconnected.

When the man power is turned off modules supporting PME# use +5V\_SB power for generating power management events.

#### 1.6.13.5 WAKE# Signal

The WAKE# signal is an open drain, active low signal that is driven low by a PCI Express function to reactivate the PCI Express Link hierarchy's main power rails and reference clocks. Only modules that support the wake process connect to this pin. If the module has wake capabilities, it must support the WAKE# function. Likewise, only systems that support the WAKE# function need to connect to this pin, but if they do, they must fully support the WAKE# function. If the wake process is used, the +3.3V\_SB supply must be present and used for this function. The assertion and de-assertion of WAKE# are asynchronous to any system clock.

If the WAKE# signal is supported, the signal is sent to the system's power management (PM) controller. Host and Device modules must provide a pull-up to +3.3V\_SB on this signal, if they are allows the signal to be used. Boards that do not use this signal are not required to drive this signal or provide pull-ups on it.

WAKE# is not PME# and should not be attached to the PCI-PME# interrupt signals. WAKE# causes power to be restored but must not directly cause an interrupt.

According to PCIe/104 specification, systems using Type 2 peripheral modules do not support WAKE# signal. For compatibility reasons some StackPC modules do not support WAKE# signal as well. Section B.3.5 describes how to get WAKE# signal always available in StackPC systems.

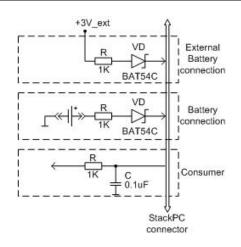

#### 1.6.13.6 RTC Battery

RTC\_Battery pin allows optional battery power for StackPC modules.

Battery cell can be placed on any module in the stack with its own resistor and diode as shown on Figure 1-6.

Battery power can be used by any module (consumer) in the stack. For longer battery life it is recommended that total battery current is less than 5 uA. RC-filter for each consumer is required.

Figure 1-6: Example of using Battery power in StackPC stack.

## 1.7. References

The following documents should be used as reference for a detailed understanding of the overall system requirements. For latest revisions of the above specifications contact the respective organizations.

|                                              | 1                          |                    |

|----------------------------------------------|----------------------------|--------------------|

| ATX Specification Version 2.2                | Intel Corporation          | www.intel.com      |

| Low Pin Count Interface Specification        | Intel Corporation          | www.intel.com      |

| Revision 1.1                                 |                            |                    |

| PC/104 Specification Version 2.5             | PC/104 Embedded Consortium | www.pc104.org      |

| PC/104-Plus Specification Version 2.0        | PC/104 Embedded Consortium | www.pc104.org      |

| PCI-104 Specification Version 1.0            | PC/104 Embedded Consortium | www.pc104.org      |

| PCIe/104 & PCI/104-Express                   | PC/104 Embedded Consortium | www.pc104.org      |

| Specification Version 2.0                    |                            |                    |

| PCI Local Bus Specification Revision 2.2     | PCI Special Interest Group | www.pcisig.com     |

| PCI Express Base Specification Revision      | PCI Special Interest Group | www.pcisig.com     |

| 1.1                                          |                            |                    |

| ExpressCard Standard Release 2.0             | USB Implementers Forum     | www.usb.org        |

| Serial ATA Revision 3.0 Specification        | SATA International         | www.sata-io.org    |

|                                              | Organization               |                    |

| Serial Peripheral Interface (SPIV3) Block    | Freescale Semiconductor    | www.freescale.com  |

| Description V3.06                            |                            |                    |

| System Management Bus (SMBus)                | SBS Implementers Forum     | www.sbs-forum.org  |

| Specification Version 2.0                    |                            |                    |

| Universal Serial Bus (USB 2.0) Specification | USB Implementers Forum     | www.usb.org        |

| Revision 2.0                                 |                            |                    |

| Universal Serial Bus 3.0 (USB 3.0)           | USB Implementers Forum     | www.usb.org        |

| Specification Revision 1.0                   |                            |                    |

| Ethernet IEEE 802.3 Standard                 | IEEE Standards Association | standards.ieee.org |

Table 1-2: References

If errors are found in this document, please send a written copy of the suggested corrections to the publishers listed on the title page.

## 1.8. Signal Naming Convention

Signals on StackPC and FPE connectors are named so that signal groupings are obvious. The fields in a signal name go from general to specific.

The PCI Express signals start with the characters "PE," followed by the width of the Link ("x1", "x4"), followed by an underscore "\_". Next is the Link number if there is more than one Link of that width. Then there is either "T", "R", or "CLK" for Transmit, Receive, or Clock respectively. Next is the lane number in the link in parenthesis, for the links that have more than one lane. The last symbol is "p" or "n" for the

positive and negative signal in the differential pair. For example, PEx4\_0T(2)p is the positive signal in lane number 2 of the first x4 Link.

A signal on the connector is designated "transmit" or "receive" in a Host-centric manner. The "transmit" pin on the Host connects to the "T" (transmit) pin of the connector. From there, the signal connects to "receive" pin of the Device.

In a PCIe system the transmit pins of the chip are always connected to the receive pins of the other chip in the link, and vice-versa. For example, for a specific link, transmit on the Host chip is connected to receive on the Device chip, and receive on the Host is connected to transmit on the Device.

Other non-PCIe signals (SATA, LPC, SPI, FBUS, Display port) follow a similar convention.

## 2. EXPANSION CONNECTOR A (StackPC)

Expansion Connector A is the main connector containing basic set of modern interfaces. It is self-sufficient and can be the only connector in most embedded designs with StackPC architecture.

## 2.1. Functions

- Four x1 PCle

- One x4 PCle

- Six USB 2.0

- Two SATA

- Two Gigabit Ethernet

- LPC

- SPI with three Slave Select lines

- SMB

- Two FBUS

- ATX power and control signals: +5V\_SB, PS\_ON#, POWERGOOD

- Power: +3.3V, +5V, +12V, RTC\_Battery

Since not all chipsets support all defined interfaces, it is up to the Host vendor to determine the type and number of implemented interfaces. However, implemented interfaces must comply with the pin out described below for Expansion Connector A. This will ensure that any peripheral module with, for example x1 PCI-Express Links will work with any Host that supports x1 PCI-Express Links.

## 2.2. Pin Assignment

StackPC connector has odd numbered pins located towards the edge of the board while even numbered pins are located towards the center of the board. Pin assignment is defined in Table 2-1.

Top View of Signal Assignment for StackPC connector for **Host & Peripheral** boards is shown on the left Column in Table 2-1.

Bottom View of Signal Assignment for StackPC connector for **Peripheral** boards is shown on the right Column in Table 2-1.

**Note**: StackPC connector is allowed only on Top of Host modules thus providing support for stacking StackPC peripheral modules only on Top of Host module.

ower Supp ous Interface SPI Bus Bus Interface PC Bus

|                                 | StackPC Assignmen              | t, To     | p View (Connector A)        |            |          |           |            | StackPC Assignment,         | Botto     | om View (Connector A)          |            |

|---------------------------------|--------------------------------|-----------|-----------------------------|------------|----------|-----------|------------|-----------------------------|-----------|--------------------------------|------------|

| 1                               | USB_OC#                        |           | PE_RST#                     | 2          |          |           | 2          | PE_RST#                     |           | USB_OC#                        | 1          |

| 3                               | 3.3V                           |           | 3.3V                        | 4          |          | 1         | 4          | 3.3V                        |           | 3.3V                           | 3          |

| 5                               | USB_1p                         |           | USB_0p                      | 6          |          |           | 6          | USB_0p                      |           | USB_1p                         | 5          |

| 7<br>9                          | USB_1n<br>GND                  |           | USB_0n<br>GND               | 8<br>10    | 1        | 1         | 8<br>10    | USB_0n<br>GND               |           | USB_1n<br>GND                  | 7<br>9     |

| 9<br>11                         | PEx1_1Tp                       |           | PEx1_0Tp                    | 10         |          |           | 10         | PEx1_0Tp                    |           | PEx1_1Tp                       | 9          |

| 13                              | PEx1_1Tp<br>PEx1_1Tn           |           | PEx1_0Tn                    | 14         |          | 1         | 14         | PEx1_0Tn                    |           | PEx1_1Tp                       | 13         |

| 15                              | GND                            |           | GND                         | 16         |          |           | 16         | GND                         |           | GND                            | 15         |

| 17                              | PEx1_2Tp                       |           | PEx1_3Tp                    | 18         | 1        | 1         | 18         | PEx1_3Tp                    |           | PEx1_2Tp                       | 17         |

| 19                              | PEx1_2Tn                       |           | PEx1_3Tn                    | 20         |          | 1         | 20         | PEx1_3Tn                    |           | PEx1_2Tn                       | 19         |

| 21                              | GND                            |           | GND                         | 22         | 1        | 1         | 22         | GND                         |           | GND                            | 21         |